|

| News | Experience | Projects | |

|

I'm Priyal Chhatrapati, a Machine Learning Engineer at Apple, where I develop their ML inference stack. I previously worked at NVIDIA as a Deep Learning Performance intern, helping with the biannual MLPerf inference submission. I hold a Master's degree from Georgia Institute of Technology, where I worked with Prof Callie Hao on accelerating Computer Vision/Deep learning models using FPGAs. For a brief time, I worked for a startup called Sifive. Before that, I completed my undergraduate degree with distinction at BITS, Pilani, Goa in Electronics and Instrumentation Engineering. I'm passionate about Artificial Intelligence and its intersection with Computer Architecture and Systems, and have also dabbled in areas like Hardware Security and DNA-based Storage. In my free time, I'm an avid sports fan, following Manchester United (Football/soccer), LA Rams (American Football), Dodgers and Braves (Baseball(MLB)), Golden State Warriors (Basketball(NBA)) and McLaren (Formula 1). I was fortunate enough to attend Austin Grand Prix, 2021 and get a Bay Grandstand seat for the Singapore Grand Prix, 2019. I'm also a big fan of anime, with One Piece and Cowboy Bebop being among my favorites. Check out my CV and feel free to email me if you'd like to chat! Check out my CV and drop me an e-mail if you want to chat with me! |

|

Dec'22 - Present Developing Machine Learning Inference stack for Apple Devices. |

|

May'22 - Aug'22 Working in the MLPerf TensorRT team to optimize Deep Learning Inference on NVIDIA GPU chips. |

|

August'21 - May'22 Working with Prof. Callie Hao at the Department of Electrical and Computer Engineering at Georgia Tech. We work on accelerating Computer Vision Workloads using Hardware. |

|

September '20 - June '21 Worked on functional Verification and RTL design for building the next generation of RISC-V enabled Microprocessors. |

|

Aug '19 - Dec '19 Worked with Prof. Djordje Jevdjic at the School of Computing at National University of Singapore. We built an approximate storage framework for images and videos for the DNA Data Storage paradigm. |

|

May '19 - June '19 Worked under the supervision of Prof. V. Kamakoti at Shakti Processor Group, IIT, Madras. We built a CNN Inference accelerator which used a systolic array architecture to reduce the compute time of Convolutions. |

|

May '18 - July '18 Worked with the Security and Innovation Sensors Division to dvelop an embedded system around the quasi digital sensors to measure, control and transmit the density and turbidity of a fluid. |

|

A trace-based simulator is one that consumes a file of load-store instructions and uses that information to fuel a simulation by calculating metrics like miss rate. My C++ implementation is reconfigurable and accepts cache capacity, blocksize and associativity as command line arguements. It uses a write back policy for write hits, write allocate policy for write misses and a LRU replacement policy for eviction. |

|

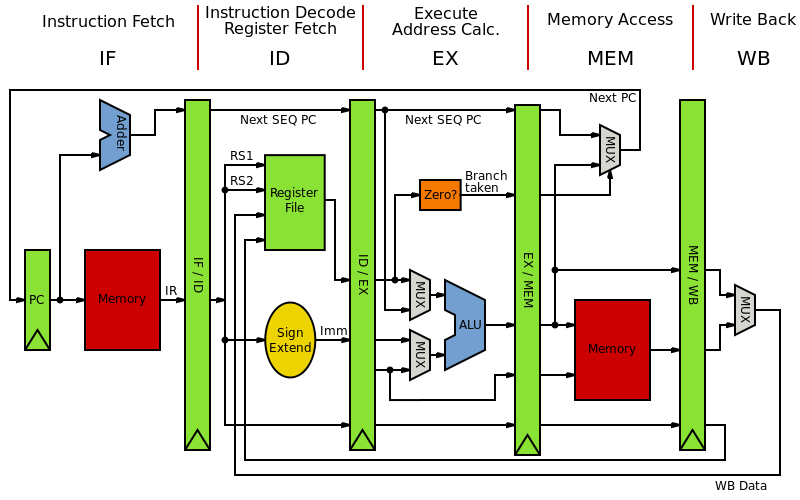

A 4 staged 8 bit MIPS ISA based processor implemented in Verilog. The processor has 8 registers (R0-R7). It supports addition, jump and unconditional jump operations. It resolves data hazards using forwarding and control hazards by flushing the pipeline. |

|

Chat Client where the reciever process uses the Flush Reload attack to spy on the sender process to extract the message. Flush Reload is a Side channel attack on the Last Level of the Cache. The sender and receiver donot share any memory or use any IPC and sockets to communicate with each other. The "Evil" chat client breaks process isolation provided by the Operating System. |

|

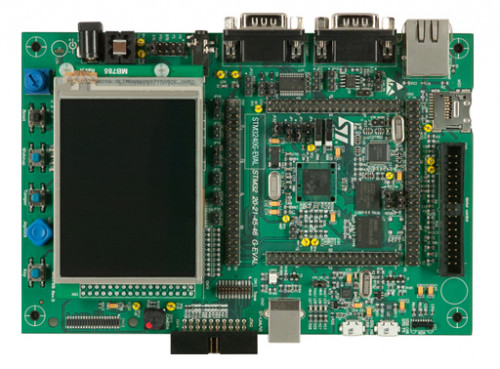

Fun Math game for elementary school students using an STM32 evaluation board, a keypad and a display. Asks random arithmetic questions using RTC, increasing the difficulty overtime. |

|

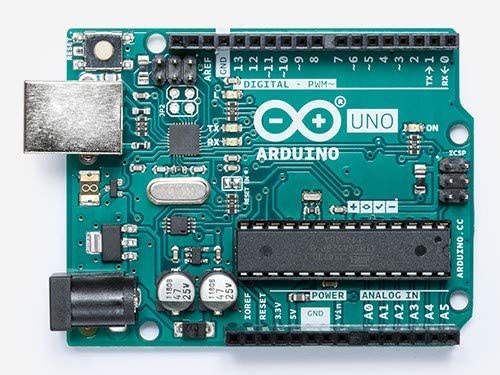

Arduino controlling the light and fan speed based on input from the temperature sensor and light sensor. Manual control using switches and pot interfaced with Arduino and/or through a website. |

This website is a modification of Jon Barron's website. Find the source code to my website here.